RISC-V指令集架构

- RISC-V

- 2024-04-27

- 815热度

- 0评论

简介

RISC-V是一个通用的指令集架构(ISA),ISA是底层硬件电路面向上层软件程序提供的一层接口规范,ISA定义了:

- 基本数据类型,BYTE/HALFWORD/WORD

- 寄存器

- 指令

- 寻址模式

- 异常或中断处理方式

之所以需要ISA,是为上层软件提供一层抽象,制定规则和约束,让编程者不用关心具体的电路结构,目前的指令集架构有两种类别:

- CISC复杂指令集(Complex Instruction Set Computing),这类指令针对特定功能的实现需要新增实现特定的指令,导致指令数目比较多,但生成的程序长度相对较短;

- RISC精简指令集(Reduced Instruction Set Computing),只定义常用指令,对复杂的功能采用常用指令组合实现,这导致指令数目比较精简,但生成的程序长度相对较长。

ISA的宽度指定是CPU中通用寄存器的宽度,决定了寻址的范围大小以及数据运算的能力。当前ISA有以下

- X86

- SPARC

- POWER

- ARM

- MIPS

- RISC-V

RISC-V ISA命名格式为RV[###][abc...xyz],如RV64IMA;

- RV:标识RISC-V体系结构前缀

- [###]:{32,64,128}用于标识处理器的子宽,即处理器寄存器的宽度,单位为bit

- [abc...xyz]:标识处理器支持的指令集模块集合,见下描述

RISCV-ISA指令集按照模块来划分,=1个基本整数指令集+多个可选拓展指令集

- 整数指令集(interger):强制要求实现的基础指令集,RV32I,RV64I

- 扩展指令集:M为整数乘与除法指令集,A存储器原子指令集,F单精度浮点指令集,D双精度浮点指令,兼容F,C压缩指令集。而GC代表IMAFDC的组合。

根据以上RV32IMAC表示32位实现,支持interger,multiply,atomic,compressed;RV64GC,就是表示支持RV64位IMAFDC。

指令集

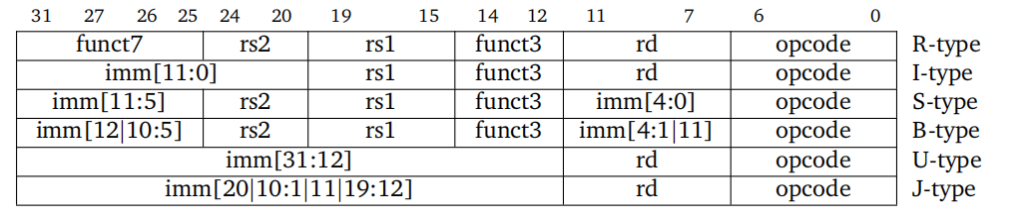

RISC-V的指令集可分为6中,每种的编码格式如下:

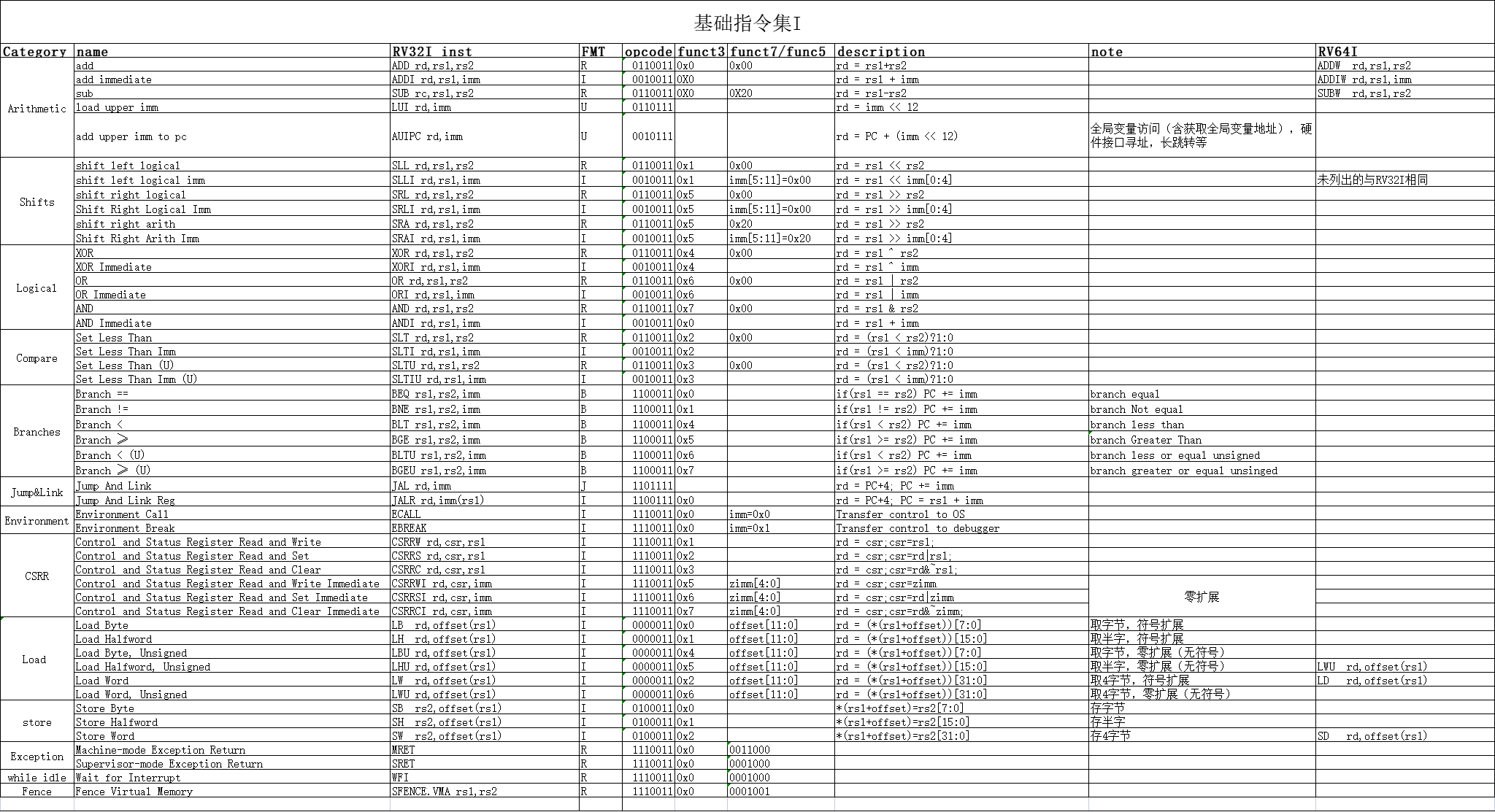

整形指令集

乘除指令集

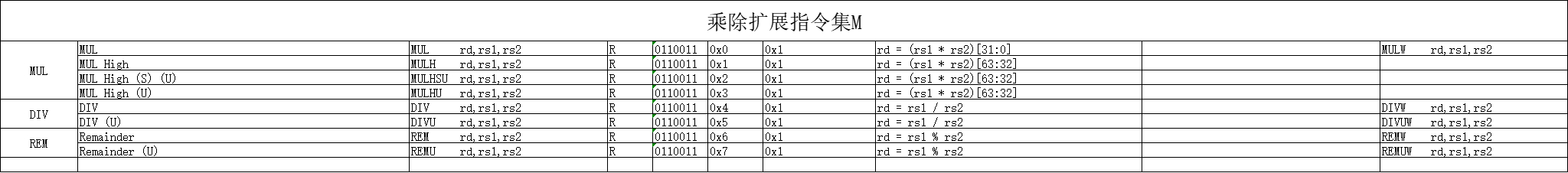

原子扩展指令集

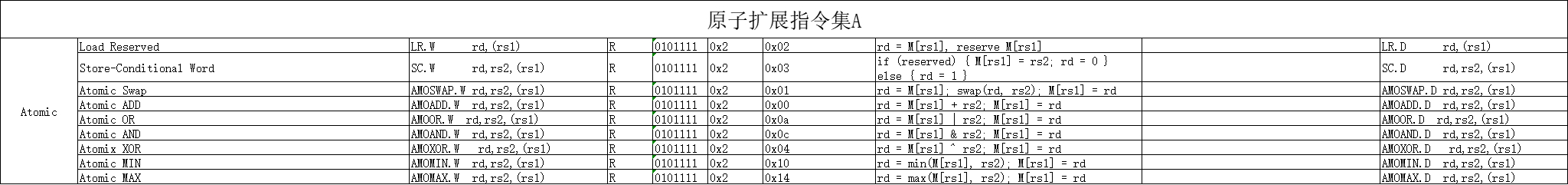

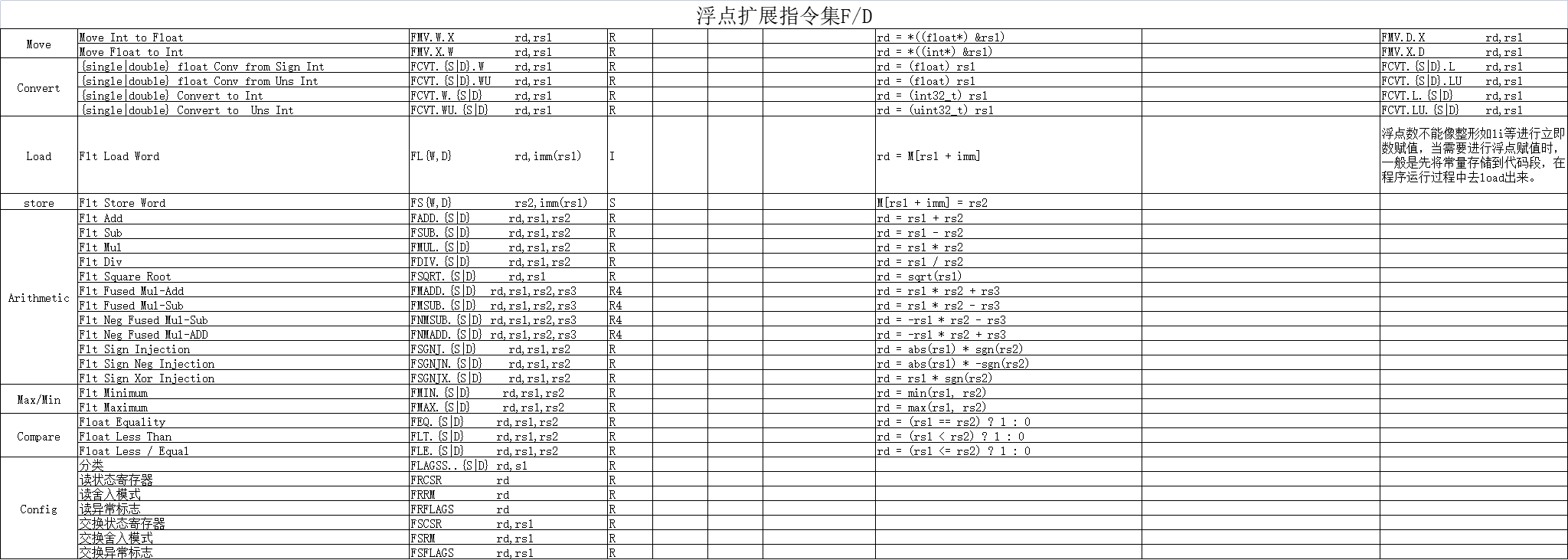

浮点扩展指令集

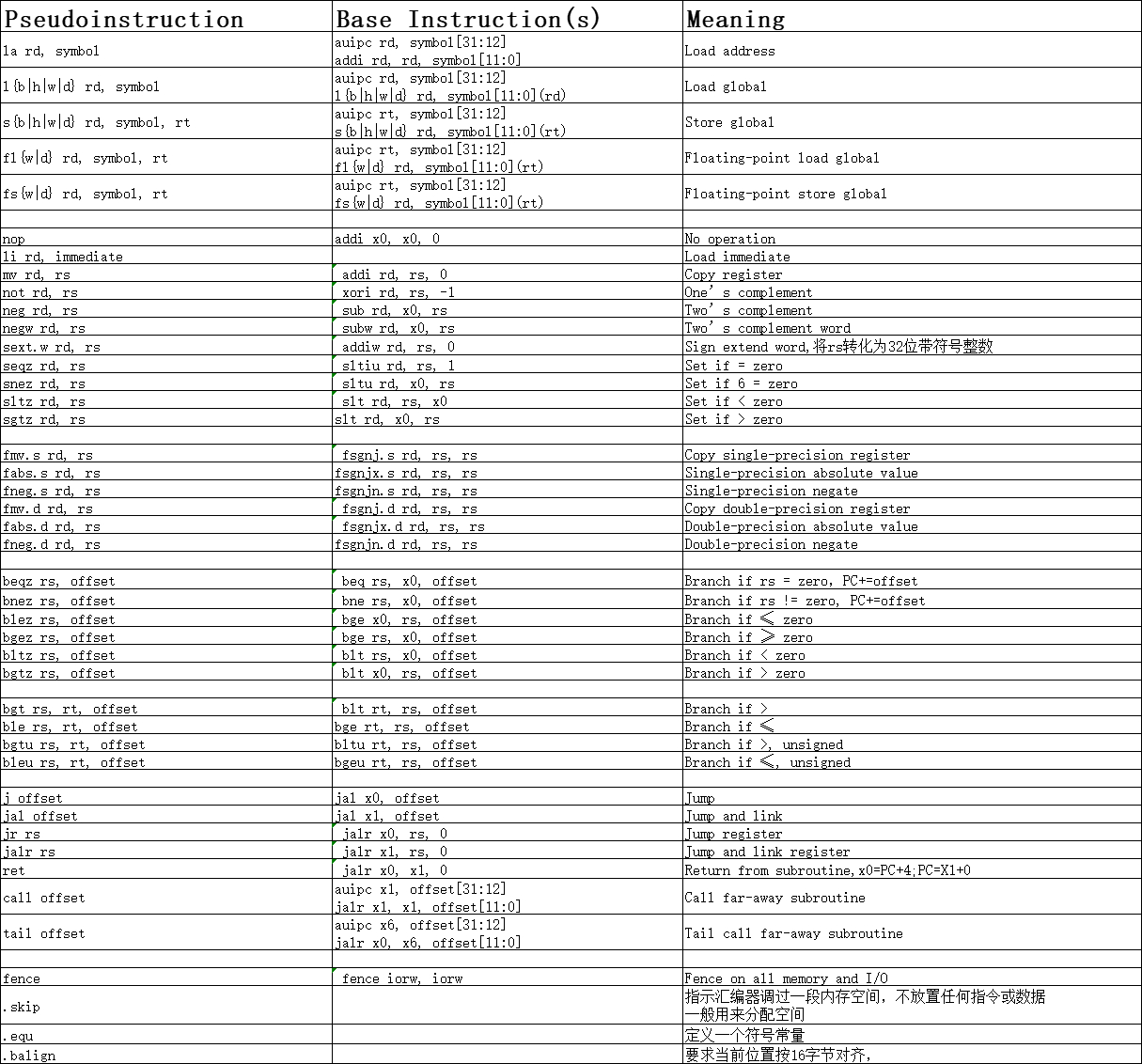

伪指令

为了方便编程,对指令进一步封装,形成伪指令

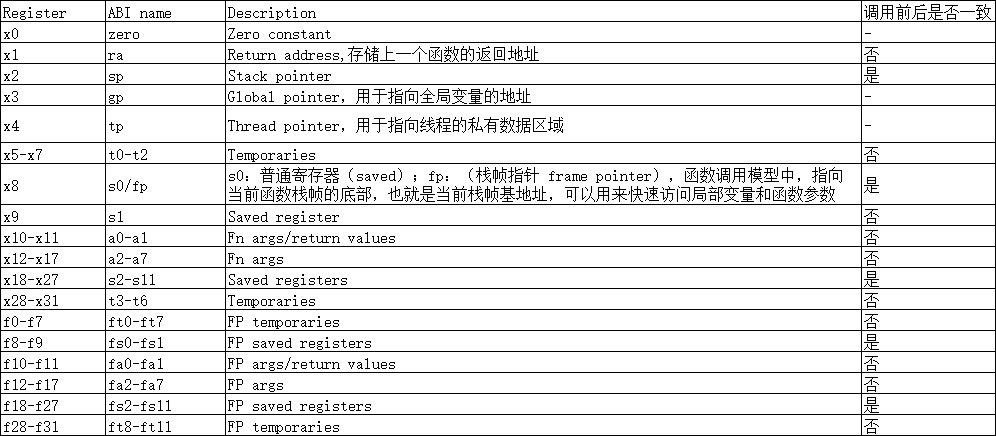

寄存器

通用寄存器

特权寄存器

RISC-V指令运行,根据访问权限,分为M/S/U模式,每个模式下有自己对应的寄存器,这里重点列出M模式相关的寄存器。

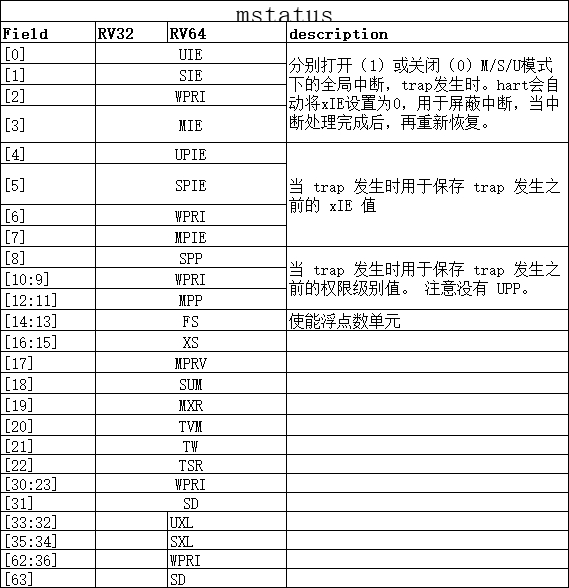

mstatus寄存器

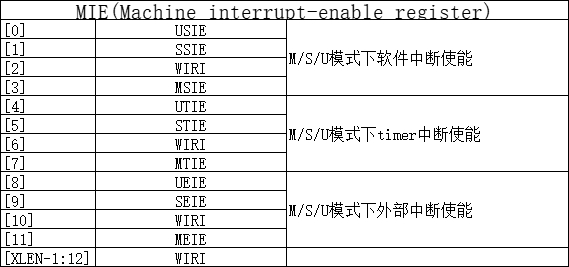

mie寄存器

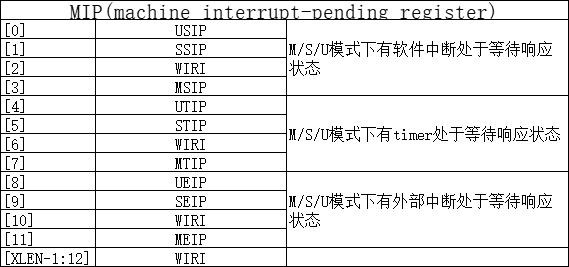

mip寄存器

mtvec寄存器

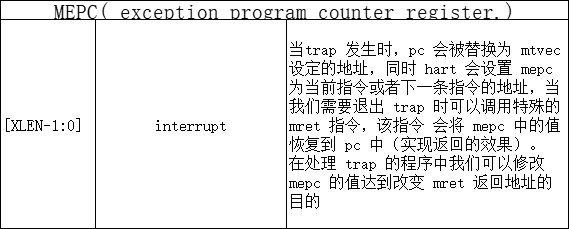

mepc寄存器

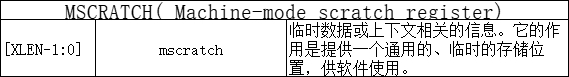

mscratch寄存器

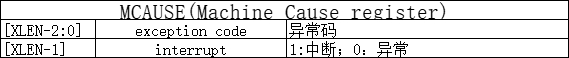

mcause寄存器

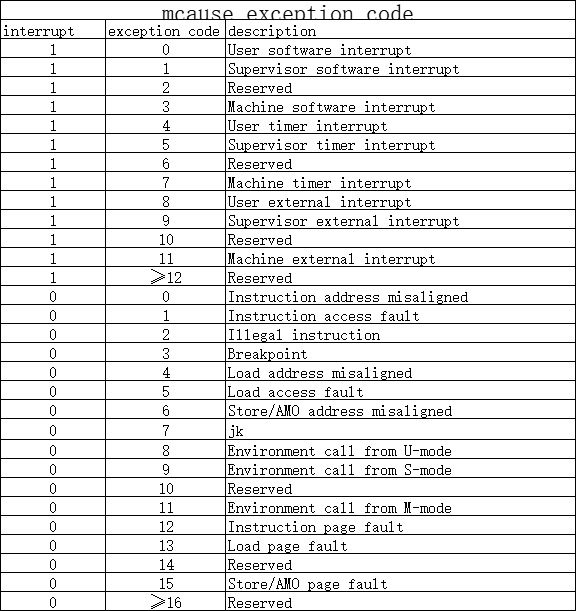

对于mcause exception code如下: